汕尾EMMC邏輯分析儀廠家

簡單觸發示例:請看下面顯示的“D”觸發器,在正值的時鐘沿出現之前,“D”輸入上的數據是無效的。因此,時鐘輸入為上限時,觸發器的狀態才有效。圖8D觸發器現在,假設我們有并行的八個此類觸發器。如下所示,這八個觸發器都連接到同一時鐘信號。圖9接收器當時鐘線上出現高電平時,所有這八個觸發器都會在其“D”輸入處采集數據。此外,每次時鐘線上出現正電平時都會發生有效狀態。下面的簡單觸發指示分析儀在時鐘線上出現高電平時在D0-D7這幾條上收集數據。圖10總線收集的數據高級觸發示例:假設想查看地址值為406F6時內存中存儲了哪些數據。對高級觸發進行配置,以在地址總線上查找碼型406F6(十六進制)以及在RD(內存讀取)時鐘線上查找高電平。圖11高級觸發設置在配置EdgeAndPatterntrigger(時鐘沿和碼型觸發)對話框時,嘗試將該操作看作是構造從左向右讀取的句子。Pod、通道和時間標簽存儲Pod和通道的命名約定:Pod是一組邏輯分析儀通道的組合,共有17個通道,其中數據16個通道,時鐘1個通道。邏輯分析儀的通道數是Pod數的倍數關系。34通道的邏輯分析儀對應兩個Pod,68通道邏輯分析儀對應4個Pod,136通道邏輯分析儀對應8個Pod。對于模塊化的邏輯分析儀。協議分析儀/訓練器廠家直銷就找歐奧!汕尾EMMC邏輯分析儀廠家

如果你想進一步了解有關它的其他方面的實際性能,不妨繼續關注小編后期帶來的更多相關測評哦。時間:2020-04-23關鍵詞:顯示器色彩均勻性vp3481優派VP3481顯示器灰階測評本文將對優派VP3481顯示器的灰階予以測評,一起來了解下吧。具體測評數據如下:灰階方面,顯示器在40%-100%的亮度下表現平穩,基本是在7400K左右,由此可見,優派VP3481顯示器色溫整體偏冷。以上便是小編此次帶來的優派VP3481顯示器灰階相關測評,此外,如果你想進一步了解有關它的其他方面的實際性能,不妨繼續關注小編后期帶來的更多相關測評哦。時間:2020-04-23關鍵詞:顯示器灰階vp3481優派VP3481顯示器色調響應度測評本文將對優派VP3481顯示器的色調響應度予以測評,一起來了解下吧。具體測評數據如下:色調響應方面,已測量的黑色曲線應該盡量和淺藍色的“光度”曲線保持一致,可以看到實測的黑色曲線和“光度”曲線幾乎完全重合,色調響應表現非常好。以上便是小編此次帶來的優派VP3481顯示器色調響應度相關測評,此外,如果你想進一步了解有關它的其他方面的實際性能,不妨繼續關注小編后期帶來的更多相關測評哦。無錫SDIO邏輯分析儀收費I3C協議分析儀/訓練器找歐奧!

因為傳遞過來的信號幅度比較小。圖23探頭的信號完整性考慮探頭的負載效應主要分為兩種類型:直流負載和交流負載。直流負載:探頭看起來象一個對地的直流負載,一般是20K歐姆。如果被測總線具有弱上拉或弱下拉特性(即上下拉電阻較),這個負載可能會導致邏輯錯誤。直流負載主要由探頭尖的電阻決定,這個電阻阻值越,直流負載越小,阻值越小,直流負載越。交流負載:探頭包含寄生電容和電感。這些寄生參數會減小探頭帶寬和導致信號反射。我們需要在被測電路接收端和探頭尖處考慮信號完整性。探頭帶寬被降低主要來自2個方面:探頭電容和探頭與目標連接的連線的電容。探頭導致信號反射的原因是4個方面:探頭電容和電感。探頭在被測總線上的探測位置;總線的拓撲結構;探頭和目標間連線的長度。對于交流負載,我們需要考慮:探測點在傳輸線的位置,總線的拓撲結構和探頭和目標間連線的長度。探頭的負載除了可以用復雜的Spice模型仿真分析外,也可以用簡單的RC模型簡單預估負載效應。下圖是典型探頭的RC模型。圖24常用探頭的RC模型我們需要仔細考慮探頭和目標之間的連線。為了可靠的電氣連接,有三種方式可選擇:短線探測(StubProbing),阻尼電阻探測。

USBtypeC等高速協議抓取和分析的服務。序列步驟存儲總會覆蓋默認存儲,但只針對序列步驟存儲中特別指定的條件。處理默認存儲和序列步驟存儲之間的時一定要謹慎。雖然設置邏輯分析儀很困難,但觸發函數可以降低此過程的難度。觸發函數是可以組合起來設置觸發的常用構建塊。由于這些函數涵蓋了多數普通觸發,因此通過選擇適當的函數并將其填充到數據中即可設置觸發。下圖顯示了邏輯分析儀觸發用戶界面。請注意,觸發函數位于屏幕左側的一個醒目位置。圖21使用觸發函數通常,設置復雜觸發的難題是對問題進行分解。換句話說,就是如何將復雜觸發映射到序列步驟、分支和布爾邏輯表達式。將問題分解為不同時發生的事件。這些事件對應于序列步驟。掃描觸發函數列表,嘗試找出一些與步驟1中確定的事件相匹配的函數。將所有剩余事件分解為布爾邏輯表達式及其相應操作。各個布爾邏輯表達式/操作對分別對應于序列步驟中的一個單獨分支。請記住,可能存在只用于為序列步驟處理存儲限定的“存儲”分支。設置邏輯分析儀觸發與編寫軟件相徑庭。如果使用預定義的觸發函數和較早編寫的文檔完善的觸發來完成其他工作,就可降低設置邏輯分析儀觸發的難度。在沒有其他可用的資源時。SD協議分析儀/訓練器廠家那家好?找歐奧!

邏輯分析儀基礎邏輯分析儀是一種類似于示波器的波形測試設備,它可以監測硬件電路工作時的邏輯電平(高或低),并加以存儲,用圖形的方式直觀地表達出來,便于用戶檢測和分析電路設計(硬件設計和軟件設計)中的錯誤。邏輯分析儀是設計中不可缺少的電子測試設備,通過它可以迅速地定位錯誤、解決問題、達到事半功倍的效果。一、邏輯分析儀的產生和發展20世紀70年代初研制出微處理器,出現4位和8位總線,傳統示波器的雙通道輸入無法滿足8bit的觀察。微處理器和存儲器的測試需要不同于時域和頻域儀器,所以數域測試儀器應運而生。當時的HP公司推出狀態分析儀和Biomation公司推出定時分析儀(兩者初很不相同)之后不久,用戶開始接受這種數域測試儀器作為終解決數字電路測試的手段,不久狀態分析儀與定時分析儀合并成邏輯分析儀。20世紀80年代后期,邏輯分析儀變得更加復雜,使用起來也更加困難。例如,引入多電平樹形觸發,以應付條件語句如IF、THEN、ELSE等復雜事件。這類組合觸發必然更加靈活,同時對大多數用戶來說就不是那樣容易掌握了。邏輯分析儀的基本發展趨勢是計算機與儀器的不斷融合。在PC機平臺上使用Windows,只要給定正確的軟件和相關工具。訓練器源頭工廠,一手勁爆價,就找歐奧!嘉興I2C/SPI邏輯分析儀電話

UniPro協議分析儀/訓練器找歐奧!汕尾EMMC邏輯分析儀廠家

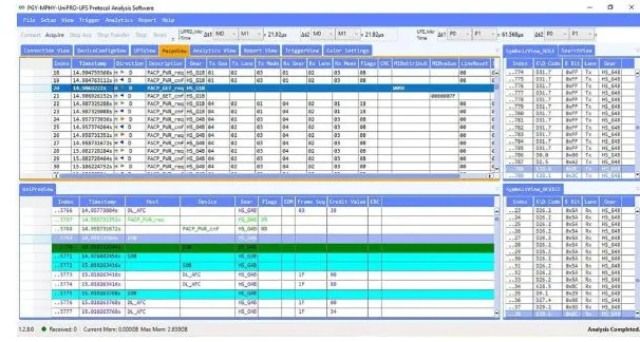

終比較結果將對“差分信號高于Vref還是低于Vref?”的問題作出解答:對眼隙的eyescan測量是通過使用不同Vref設置進行一系列eyefinder測量完成的。差分信號的默認eyefinder測量使用Vref=0V。通過將Vref增至零以上。歐奧電子是Prodigy在中國區的官方授權合作伙伴,ProdigyMPHY,UniPro,UFS總線協議分析儀測試解決方案不會收到EAR進出口方面的管制。同時還有代理其他總類的協議分析儀,包括嵌入式設備用的SDIO協議分析儀,QSPI協議分析儀及訓練器,I3C協議分析儀及訓練器,RFFE協議分析儀及訓練器等等。我司還有代理SPMI協議分析儀及訓練器,車載以太網分析儀,以及各種相關的基于示波器的解碼軟件和SI測試軟件。同時,歐奧電子也有提供高難度焊接,以及高速信號。如UFS,DDR3/DDR4,USBtypeC等高速協議抓取和分析的服務。我們會找到信號與上升的Vref值交叉的位置。如果Vref升至足夠高,信號的頂部軌跡將通過Vref,我們便會看到眼的頂端。再將Vref升高一點會導致Vcomp保持在Vlo,表示信號不會升至該電之,將Vref移至零以下會看到眼的下半部。eyescan/eyefinder顯示窗口會在每個信號的eyescan圖下方顯示eyefinder交疊部分,以此顯示eyefinder與eyescan之間的這一關系。汕尾EMMC邏輯分析儀廠家

- 梅州UFS協議分析儀售價 2025-04-15

- 陽江USB協議分析儀售價 2025-04-15

- 福州UART協議分析儀電話 2025-04-15

- 南通SDIO邏輯分析儀 2025-04-15

- 惠州SDIO邏輯分析儀找哪家 2025-04-15

- 黃石I3C協議分析儀價格 2025-04-15

- 溫州SDIO協議分析儀費用 2025-04-15

- 汕頭I2C/SPI協議分析儀找哪家 2025-04-15

- 株洲UFS協議分析儀那家好 2025-04-15

- 蘇州I3C邏輯分析儀品牌 2025-04-15

- 云南智能化GRACO供料系統品牌代理 2025-04-15

- 上海真空計生產廠家 2025-04-15

- 山東萊蒙蒸汽品質檢測儀廠家電話 2025-04-15

- 浙江專注表面溫度計供應商 2025-04-15

- 意大利HSW流量傳感器性價比 2025-04-15

- 無錫電學計量價格 2025-04-15

- 中山電源模塊有哪些 2025-04-15

- 北京污水流量計品牌排行 2025-04-15

- 河南常見ABB接觸器品牌排行 2025-04-15

- 安徽機械振動分析儀 2025-04-15